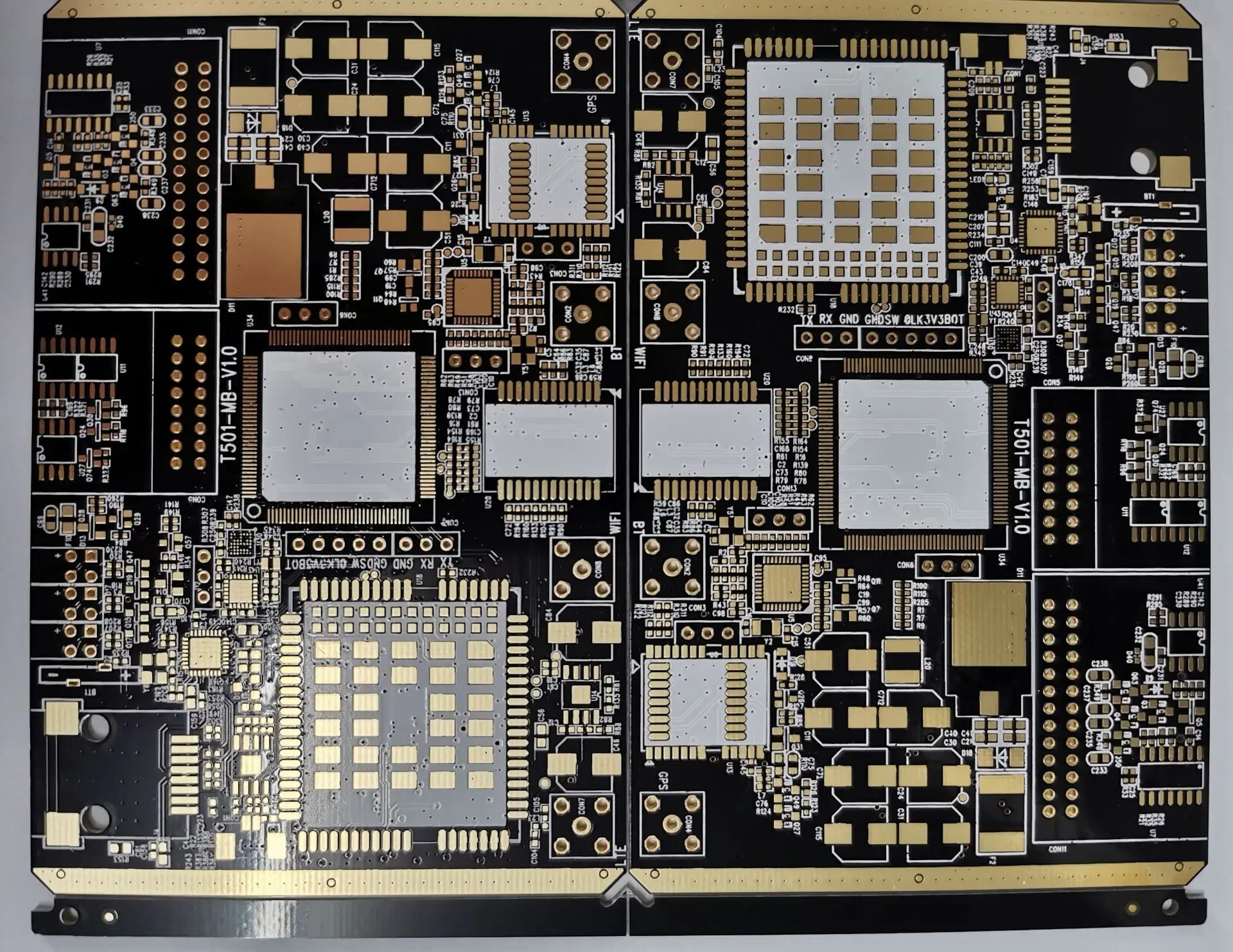

PCBA元件布局间距设计

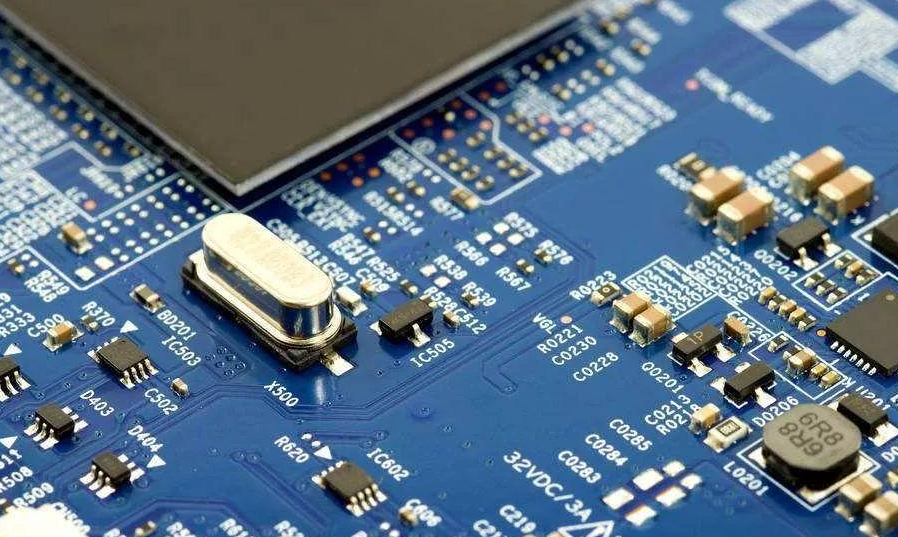

在现代电子设计中,PCBA(印刷电路板组件)的元件布局间距远非简单的几何排列,而是融合电气安全、热力学、信号完整性及制造工艺的系统性工程。元件间距的毫厘之差,可能引发信号串扰、散热失效甚至高压击穿。

一、电气安全间距

电气安全间距的核心使命是防止电弧击穿和漏电事故,其数值由工作电压、环境污秽等级及绝缘材料共同决定。根据IPC-2221标准和IEC 60950-1安全规范:

低压电路(0-30V):导线间距最小0.1mm(4mil),例如手机主板中CPU与内存间的布线。

中压电路(30-150V):遵循公式 间距(mm)=0.1+Vpeak×0.01,如48V工业电源板需≥0.58mm。

高压电路(>150V):一次侧交流线路间至少2.5mm(如开关电源L-N间距),一次侧与二次侧间需≥6.4mm,并在光耦下方开隔离槽。

极端环境补偿:海拔2000米以上设备,间距需倍增1.48倍;盐雾环境则需通过三防漆将爬电距离提升300%。

集成电路引脚间距的极限挑战出现在0.4mm pitch QFP封装中——焊盘宽度仅0.2mm,间隙0.2mm,需在焊盘间铺设阻焊桥并严格控温,避免回流焊时桥连。

二、元件物理间距

1. SMD器件间距法则

同类型器件:0201电阻电容间距≥0.3mm,避免焊膏粘连。

异型器件:按 0.13H+0.3mm 计算(H为相邻元件高度差),如3mm高电解电容旁布置2mm电感,最小间距=0.13×(3-2)+0.3=0.43mm。

密间距器件:0.5mm pitch IC焊盘宽度0.25mm,通过激光切割钢网实现锡膏精准印刷。

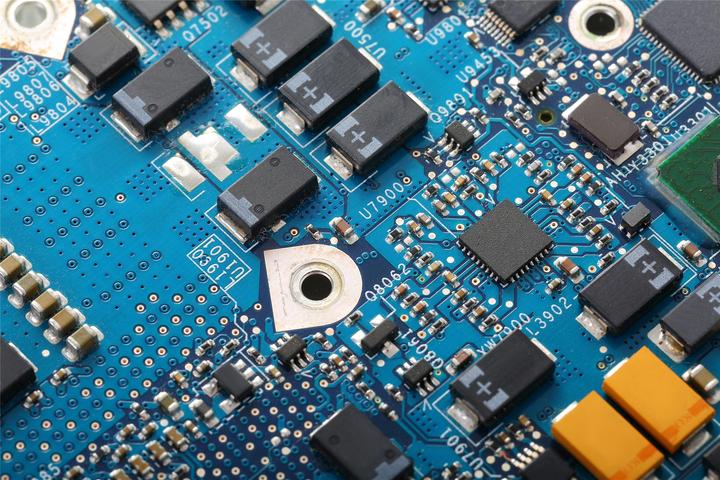

2. 特殊器件的空间禁区

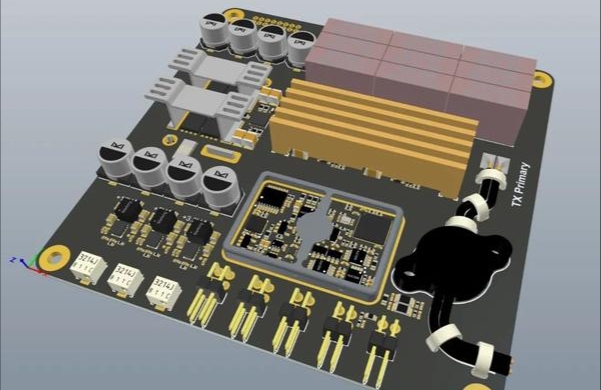

BGA封装:周边需3-5mm禁布区,背面投影区8mm内禁止放置其他BGA,防止X射线检测盲区。

大功率器件:MOSFET与散热器间距>2mm,铜箔铺设泪滴状散热通道减少热应力裂纹(泪滴宽度渐变比≤2.5:1)。

高频元件:晶振与CLK信号线间距≥3倍线宽,下方铺设地平面屏蔽辐射。

三、层叠结构与信号完整性

多层板的层间结构直接影响等效间距:

4层板黄金法则:顶层信号-内层地-内层电源-底层信号。地层为顶层信号提供镜像回路,将串扰降低至双面板的1/10。

6层板优化方案:信号1-地-信号2-电源-地-信号3。高速信号夹在两地层间,阻抗波动控制在±5%内(如DDR4布线)。

电源地耦合:电源层与地层介质厚度≤0.127mm(5mil),将谐振频率提升至GHz级,抑制电源噪声。

当差分对(如USB3.0)穿越不同层时,需添加回流地过孔阵列,间距小于λ/10(λ为信号波长),避免阻抗突变引发反射。

四、环境与工艺影响

1. 焊接工艺的硬约束

波峰焊禁区:板边3mm内禁布SMD器件,避免液态焊锡冲刷(如电源连接器周边)。

回流焊热管理:0805以上陶瓷电容轴向平行传送方向,减少热应力开裂风险。

钢网扩口需求:变压器引脚需额外0.2mm冗余间距,补偿共面性偏差。

2. 机械应力防护

板边安全区:元件离板边距离>2倍板厚(1.6mm板需≥3.2mm),防止V-CUT分板时撕裂焊盘。

高振动环境:汽车电子中QFN封装四角添加环氧树脂锚点,抗15Grms振动。

五、未来挑战

随着0.3mm pitch Wafer-Level封装(如苹果M系列芯片)普及,间距设计面临新挑战:

材料革新:低温共烧陶瓷(LTCC)基板将线宽/间距推至10μm/10μm,但需氦气环境焊接。

动态间距补偿:AI驱动的布线工具实时仿真热变形量,自动调整BGA焊球间距(如Intel EMIB技术)。

分子级绝缘:原子层沉积(ALD)Al₂O₃涂层使5kV电路间距从2.5mm缩减至0.5mm,突破IPC标准极限。

总结

电子元件的间距设计,实则是电气性能、热力学、机械强度三维约束下的最优解搜索。从高压电站的厘米级绝缘到手机芯片的微米级布线,每一寸空间的精准掌控,都是人类在微观世界构建可靠文明的科技史诗。当3D异构集成将百万晶体管压缩至方寸之间,间距设计已超越几何学范畴,升维为电子工程的核心哲学。